- 您现在的位置:买卖IC网 > Sheet目录3880 > PIC24F08KL302-I/SO (Microchip Technology)IC MCU 16BIT 8KB FLASH 28-SOIC

PIC24F16KL402

FAMILY

DS3

1037B-page

37

20

11

M

ic

rochip

T

e

chnology

In

c.

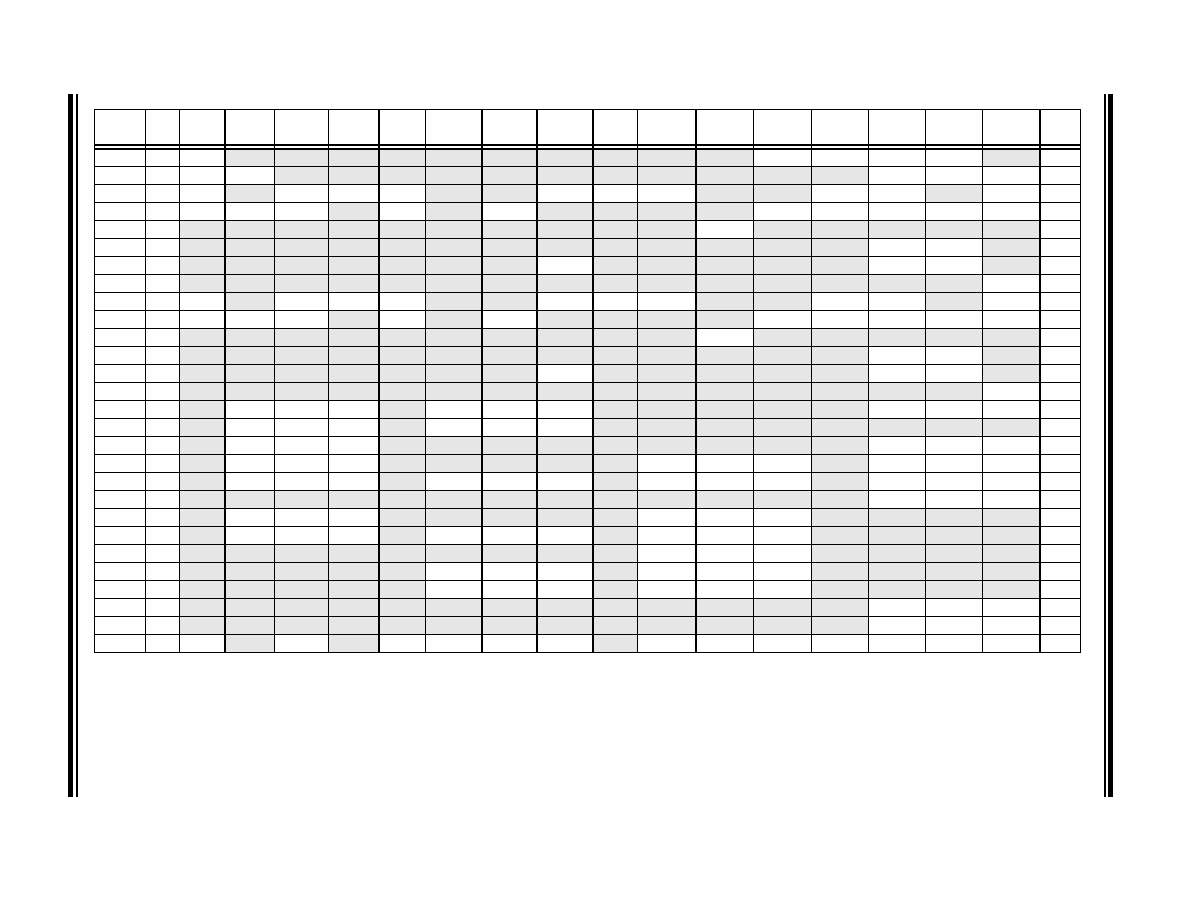

TABLE 4-5:

INTERRUPT CONTROLLER REGISTER MAP

File

Name

Addr

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

All

Resets

INTCON1 0080 NSTDIS

—

MATHERR ADDRERR STKERR

OSCFAIL

—

0000

INTCON2 0082

ALTIVT

DISI

—

INT2EP

INT1EP

INT0EP

0000

IFS0

0084

NVMIF

—

AD1IF

U1TXIF

U1RXIF

—

T3IF

T2IF

CCP2IF

—

T1IF

CCP1IF

—INT0IF

0000

IFS1

0086 U2TXIF

U2RXIF

INT2IF

—T4IF(1)

—

CCP3IF(1)

—

INT1IF

CNIF

CMIF

BCL1IF

SSP1IF

0000

IFS2

0088

—

—T3GIF

—

0000

IFS3

008A

—

—BCL2IF(1)

SSP2IF(1)

—

0000

IFS4

008C

—

—HLVDIF

—

—U2ERIF

U1ERIF

—

0000

IFS5

008E

—

—ULPWUIF

0000

IEC0

0094

NVMIE

—

AD1IE

U1TXIE

U1RXIE

—

T3IE

T2IE

CCP2IE

—

T1IE

CCP1IE

—INT0IE

0000

IEC1

0096 U2TXIE U2RXIE

INT2IE

—T4IE(1)

—CCP3IE(1)

—

INT1IE

CNIE

CMIE

BCL1IE

SSP1IE

0000

IEC2

0098

—

—T3GIE

—

0000

IEC3

009A

—

BCL2IE(1)

SSP2IE(1)

—

0000

IEC4

009C

—

—HLVDIE

—

U2ERIE

U1ERIE

—

0000

IEC5

009E

—

—ULPWUIE

0000

IPC0

00A4

—

T1IP2

T1IP1

T1IP0

—

CCP1IP2

CCP1IP1

CCP1IP0

—

INT0IP2

INT0IP1

INT0IP0

4404

IPC1

00A6

—

T2IP2

T2IP1

T2IP0

—

CCP2IP2

CCP2IP1

CCP2IP0

—

4400

IPC2

00A8

—

U1RXIP2 U1RXIP1 U1RXIP0

—

T3IP2

T3IP1

T3IP0

4004

IPC3

00AA

—

NVMIP2

NVMIP1

NVMIP0

—

AD1IP2

AD1IP1

AD1IP0

—

U1TXIP2

U1TXIP1

U1TXIP0

4044

IPC4

00AC

—

CNIP2

CNIP1

CNIP0

—

CMIP2

CMIP1

CMIP0

—

BCL1IP2

BCL1IP1

BCL1IP0

—

SSP1IP2

SSP1IP1

SS1IP0

4444

IPC5

00AE

—

INT1IP2

INT1IP1

INT1IP0

0004

IPC6

00B0

—T4IP2(1)

T4IP1(1)

T4IP0(1)

—

—

4040

IPC7

00B2

—

U2TXIP2 U2TXIP1 U2TXIP0

—

U2RXIP2

U2RXIP1

U2RXIP0

—

INT2IP2

INT2IP1

INT2IP0

—

4440

IPC9

00B6

—

T3GIP2

T3GIP1

T3GIP0

—

0040

IPC12

00BC

—

—

0440

IPC16

00C4

—

U2ERIP2

U2ERIP1

U2ERIP0

—

U1ERIP2

U1ERIP1

U1ERIP0

—

0440

IPC18

00C8

—

HLVDIP2

HLVDIP1

HLVDIP0

0004

IPC20

00CC

—

ULPWUIP2 ULPWUIP1 ULPWUIP0 0004

INTTREG 00E0 CPUIRQ

—VHOLD

—

ILR3

ILR2

ILR1

ILR0

—

VECNUM6 VECNUM5 VECNUM4 VECNUM3 VECNUM2 VECNUM1 VECNUM0

0000

Legend:

— = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

Note 1:

These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as ‘0’.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2L-0535-1

CONN FPC 5POS 0.5MM SMT

PIC18LF23K22-I/SS

IC PIC MCU 8KB FLASH 28SSOP

PIC16LF1933-I/ML

IC PIC MCU FLASH 4K 28-QFN

PIC16F1933-I/ML

IC MCU 8BIT FLASH 28-QFN

PIC16F785-I/ML

IC PIC MCU FLASH 2KX14 20QFN

XF2L-0425-1

CONN FPC 4POS 0.5MM SMT

PIC16F1933-I/MV

IC MCU 8BIT FLASH 28-UQFN

PIC16F785-I/SO

IC PIC MCU FLASH 2KX14 20SOIC

相关代理商/技术参数

PIC24F08KL302-I/SP

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/ML

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/MQ

功能描述:16位微控制器 - MCU 8KB FL 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL401

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low-Power, Low-Cost, General Purpose 16-Bit Flash Microcontrollers with nanoWatt XLP Technology

PIC24F08KL401-I/MQ

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT